Reconfigurable Microelectronic Devices (architecture, development tools, programming language)

02 — 15 JULY, 2018

If you're fond of microelectronics and programming join this summer course!

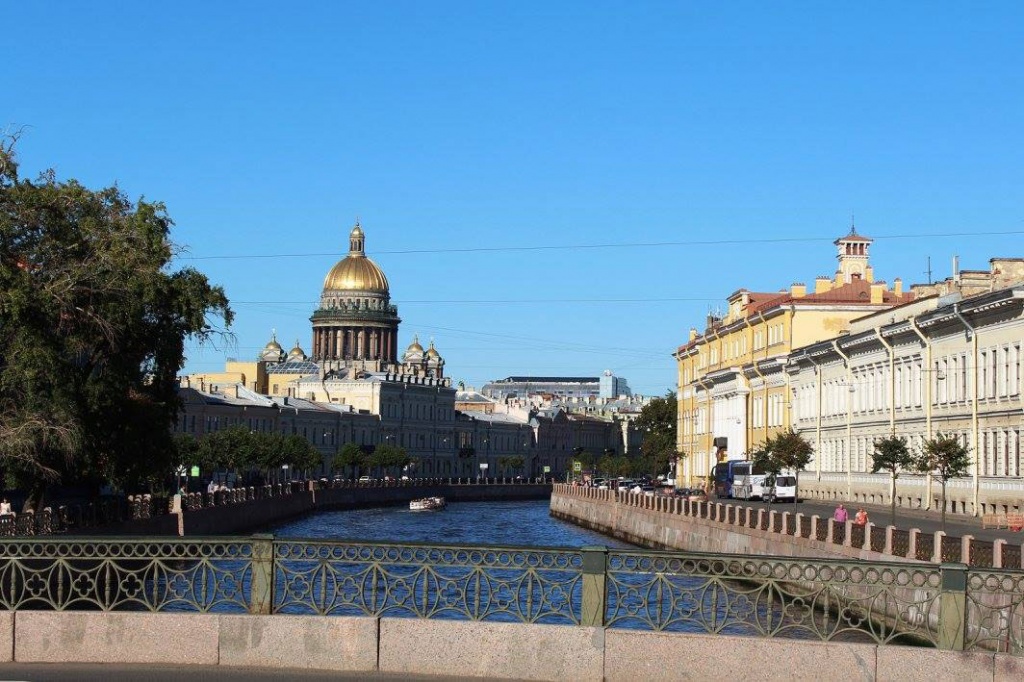

We welcome students to come to a wonderful city of St. Petersburg, the cultural heart of Russia as well as a major trade gateway, financial and industrial centre. Studying in St. Petersburg is a great experience which will contribute significantly to the student’s future success.

The course provides students with comprehensive introduction to

- FPGA architecture,

- FPGA design flow and tools

- Verilog Hardware Description Language

- FPGA programming and debugging.

Lectures and labs will be provided to introduce state-of-art tools and techniques needed to implement digital designs on FPGA platforms.

The course includes practical hands-on exercises with using FPGA development boards to implement, test, and debug your digital designs.

Students will gain theoretical knowledge and practical experience of:

- Using modern FPGAs for implementing digital designs

- Using Verilog HDL for coding digital designs

- Using Verilog HDL for coding testbenches

- Using a state-of-art tools for simulating, synthesizing, placing and routing, implementing and debugging digital designs

Program dates:

Arrival: June 29 - July 01, 2018

Classes: July 2 - 13, 2018

Departure: July 14 - 16, 2018

Duration:

2 weeks

ECTS credits: 4.0

Participation fee:

Early bird fee: 410 euro

Regular fee: 480 euro

Participation fee includes tuition fee, study materials, visits to companies and cultural program.

The cultural program includes:

- Boat city tour for students to get acquainted with the beauty of the city.

- Excursion to the Hermitage, one of the world’s largest and oldest museums of fine art.

- Visit to the “Baltika” Brewery/"Coca-Cola" factory where students can learn about the construction and logistic peculiarities of the plant.

- Picnic at the seashore of the Gulf of Finland where students can enjoy Russian style barbecue.

- Excursion to Pushkin, former tzar summer residence famous for its palace and park ensemble. Students will visit the outstanding Catherine Palace with glorious Amber room (optional, for extra price).

- Excursion to Peterhof palace-ensemble with picturesque gardens, a countless number of fountains and giant golden statues (optional, for extra price).

Deadline for registration:

Early bird deadline:

- for non-EU citizens: March 20, 2018

- for EU citizens and citizens of visa-free countries: May 02, 2018

- for non-EU citizens: April 16, 2018

- for EU citizens and citizens of visa-free countries: May 28, 2018

- A basic understanding of digital circuits and sequential logic is required.

- Good command of English. All classes and extracurricular activities are carried out in English. Knowledge of the Russian language is not required.

- Applicants are expected to have at least 2 years of University level studies.

Course description

4 ECTS

- Introduction to modern FPGAs architecture / lectures- 2 hours /

- Introduction to state-of-art design tools and FPGA based design flow / lectures – 8 hours; labs – 8 hours /

- Introduction to Verilog HDL for coding design / lectures – 12 hours; labs – 12 hours /

- Introduction to Verilog HDL for coding testbenches / lectures – 12 hours; labs – 12 hours /

- Introduction to timing analysis / lectures – 2 hours; labs – 2 hours /

- Introduction to design optimization / lectures – 2 hours; labs –2 hours /

- Introduction to design implementation and debugging / lectures – 2 hours; labs – 4 hours /

Professors and lecturers: prof. Alexander Аntonov

Program partners: ISEC EMS, Intel FPGA

Contacts

- summerschool@spbstu.ru

- +7 (812) 534-25-31

- +7 (812) 534-13-65

- room 227, 28, Grazhdanskii prospect, 195220, St.Petersburg, Russia